# THE EFFECTS OF MULTIPLE-GATED LAYOUT ON POWER CONSUMPTION OF PSEUDOMORPHIC-HEMTS

M. N. OSMAN, S. YAAKOB, M. R. YAHYA, A. F. AWANG MAT

Microelectronic & Nano Tech., TM R & D Sdn. Bhd, Malaysia

Z. AWANG

Microwave Technology Center, Universiti Teknologi MARA (UiTM), Malaysia

Abstract A study of the effects on power consumption exhibited by multiple-gated layout pseudomorphic HEMTs device is presented here. This study required that the DC parameter extraction to be carried out on the p-HEMT device with a specific number of gate layouts. From the I-V measurement, it was found that the p-HEMT that applied six gated layout can reduce 75% of power consumption as compared to two gated layout in producing the same amount of  $I_{ds}$ . This result proved that the p-HEMT device with higher number of gates consumes less power. The consequences of this lead to the reduction of device power consumption without sacrifying the device performance.

#### Introduction

The demand on the higher performance analog RF transistor device in a circuit application has led to the production of very competitive design which mainly focused on electrical characteristic improvement especially on output current, linearity, threshold voltage that gives better and higher device performance (Xu et al., 1998; Bonkee et al., 2000; Bonkee et al., 2001; Tae et al., 2004). One of the solutions to achieve this objective is by applying the multiple gated-layouts in the transistor device structure. Some researchers have done the simulation and modeling on this multiple-gated layout and found significant improvement on electrical performance of certain transistor device (Iniguez, 1999; Hon-Sum et al.,). Other researchers have also found that this multiple-gated layout also could also improve the power consumption of a transistor device and thus made the circuit more efficient (Chang et al., 2000; Dao, 2004). However, the application of this multiple-gated concept to all semiconductor devices has not been fully explored especially for pseudomorphic HEMT (p-HEMT) device. Due to the different structure, material and operation of p-HEMT device, this concept needs to be investigated further. In this study, the effect of multiple-gated layout on power consumption performance in GaAs based p-HEMT device was observed. The result obtained from the I-V measurement will be used in the power consumption analysis.

Correspondence: Mohd Nizam Osman, Microelectronic & Nano Tech., TM R & D Sdn. Bhd, Malaysia

### Material and Methods

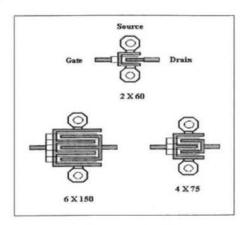

In order to study the multiple-gate layout effect on p-HEMT device power consumption, specific layout have been used. Three types of layouts were used in this experiment, comprising of 2x60, 4x75 and 6x150 layouts. The 2x60 layout represented 2-gated layout with 60-micron gate length, and the 4x75 and 6x150 layouts represented 4-gated and 6-gated with 75 micron and 150 micron

UMT, 2007

M. N. Osman et al.

gate width respectively. The gate length of all devices was 0.5 micron. The figure of those device layouts is shown in Fig. 1.

Figure 1. The layout of 2x60, 4x75 and 6x150 of p-HEMT device

Basically, the layout consists of Gate, Source and Drain terminals which are standard for p-HEMT device. The Gate terminal indicates the input and the Drain is the output terminal. In this study, the Source was connected to the common Ground at the bottom of the wafer. In other studies, the gate width for each layout was fabricated for different length. However, this variation of gate width might contribute to the performance of the device in a different way. Xu et al., (1998) found that the 4x25 layout produced poorer pinch-off characteristic compared to 2x50 layouts. Even though the total gate width is the same, they show a different performance in electrical characteristic.

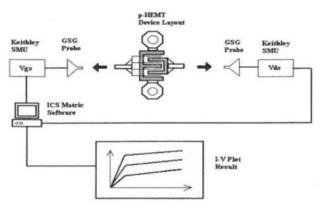

The on-wafer DC probing technique was the selected measurement setup used throughout the process of extracting the I-V characteristic. This technique was selected because the device was in a wafer form. The low parasitic GSG probe tips were used to probe on the device layout, which was ready in a GSG pad. One tip was probed on the Gate terminal that supplied the  $V_{\rm gs}$  and the other tip was probed on the Drain terminal for  $V_{\rm ds}$ . The source terminal was grounded by the chuck of the probe station. Both probe tips were connected to the Keithley Source Measure Unit (KSMU). The current flow in the device was then feedback to the analyzer to obtain the I-V characteristic of the device during the present of biasing. The basic setup for the DC measurement of p-HEMT device is shown in Fig. 2.

Figure 2. Setup during dc measurement of p-HEMT device

For the voltages setting, the drain source voltage, Va was swept from 0 V to 2 V. The gatoguarce rollage, Pm was stepped from 0.2 V to +0.3 V with the step size of 0.1 V. All the voltage settings were controlled through interactive characterization andware (ICS) metric, which commerciated to the KSMU using GPIB cable. The plot of the result was being monitored on the plot windows of this ICS matrix software. A I device begants were supplied with the same voltage softiage. The  $l_{ij}$  vs  $V_{ij}$  curve of each device layout was plotted accombingly.

## Results and Discussion

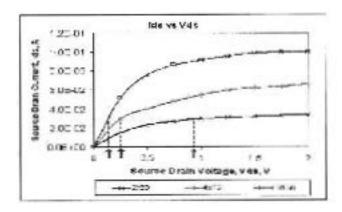

The aloc of I-V characteristic of all p-HEMT device layouts are compared at V<sub>in</sub> = 0V as shown in Fig.

Figure 3.  $I_{cs}$  vs  $V_{cs}$  at  $V_e = 0 \text{ V}$

From Fig. 3, it can be observed that the 6x150 layout produced higher source-drain current as suggested by Mohd Nizam et al., (2006). The horizontal deuted by a mithe plot shows a constant 30  $mA_{ij}$  current and the vertical dotted lines show the corresponding  $v_{ij}$  required for each layout ineader to produce that amount of current. It was found that the 6x150 inyout required only 0.13 V of hinsing voltage while the 4x75 and 2xxX layouts required 0.26 V and 0.85 V respectively. The calculation of device power consumption P is given by (1):

$$P_{Auty} = V_{A} \times I_{D}$$

(C)

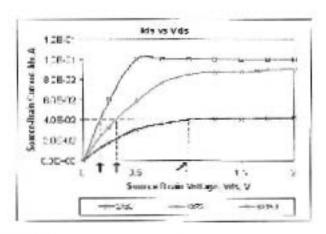

From (1), the calculation of power consumption given by 6x150 layouts to produce 30 mA L. at P<sub>2</sub> = 0 V was about 4 mW. Meanwhile the 4x75 and 2x60 were 7.8 mW and 25.5 mW respectively. Therefore, the higher purpose of eare layout consumed loss power in producing the same distin-source oursers, I<sub>L</sub>. In comparison, (x) 50 reduced power consumption more than 60% to that of 4x75 and 72% to that of 2x60 beyon. As shown in Fig. 7, the plot was obtained at elightly positive value of Ve = 0.2 V. It theres that the curve given by 6x150 was arready saturated to "DII mA due to economical limitation. However, in order to produce 49 mA lds, the 6x150 layout only required 0.16 V with prover consumption of 6.4 mW, while the 4x75 and 2x60 required 0.32 V and 1.0 V with power our complient of 12.3 mW and 40 mW respectively. Again the 6x150 layout aignificantly reduced about 30% compared to that of 4x75 and about 75% to that of 2x60.

3d. N. Coman or of

Figure 4.  $I_A \approx V_A \approx V_A = 0.2$

For the begative  $V_{ij}$ , the plot of the drain-source current is given in Fig. 5 at  $V_{ij} = 0.2 \text{ V}$ . The purpose of this sching was to observe the consistency of the power consumption at any range of easter bias. As from (1), the power consumption of 6x150 was about 3.2 mW in order to produce  $\lambda t$  and  $I_{ij}$ . Meanwhile the 4x75 and 2x60 consumed 6.4 mW and 20 mW respectively. With the radic ion of about 50% to 4x75 layout and 75% to 2x60 layout, the results undeated the consistency of the power consumption reduction of 6x150 layout at any range of bias voltage. The same parameter of power consumption activation was obtained regardless of the range of  $V_{ij}$  and  $V_{ij}$ .

Figure 5. Ly to Vo at V. = 4.2 V

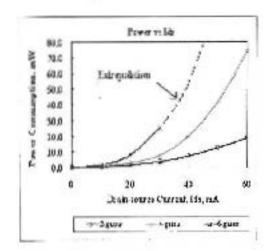

Based on previous moreon voltage relationable, the general plan of power consumption and the ide current for each layout is illustrated in Fig. 6. Figure 6 shows that the power communed by 3-quited layout is greater than the 4-quited and 6 guard layouts at any point of  $I_{\rm th}$ . The extrapolation or the 2-quited beyont (shown by denied line) is caused out in order to demonstrate the differences in power consumption by the nucleus

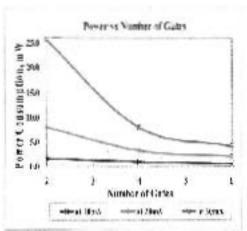

Another comparison on the relationship between the power consumption and the number of gares is illustrated in Fig. 7. From Fig. 7, it is clearly observed that as the number of gare increases, the power consumption decreases, and even lower at smaller value of  $I_{\rm co}$ .

Figure 6. Power vs In at V. -- J V

Figure 7. Power vs no. of gues-

#### Conclusion

By measurement, it was proven that multiple-gated layout applied in p-HEMT covice was the best procedure to solve high power consumption problem in current ussign. The higher the number of gates, the more power could be reduced significantly. This finding also supported the common undermedian reporting the advantage of archiple-good layout as obtained in other semiconductor device like FET, MESPET and MOSFET. The capability of multiple-gated layout p-HEMI device in reducing enters big percentage in power consumption while maintaining the performance rules this concept applicable to most RF circuit systems.

## Acknowledgments

The nurber would like to thank TM Research & Development Sdn. Bird. and MTC, UiTM for providing the facilities and expertise in the implementation of this research.

## References

Hurjamin Inlignez, 1999, IEEE Trans. On Electron Device 46(8):1742-1748.

Honkon Kirn, Jio-Su Ko and Kwyro Lee, 2000. IEEE Microway and Guided Wave Letters 10(9):371-

Bonkov Kim, Jin Sa-Ko and Kwyro Lee, 2001. IPEE MTT-S Digest 5, 5-518 pp.

Chang, E. Y., Dr. Joung Lee, S. H. Chen and J. C. Chang. 2000. Ploetronies Letters 36(4) 577-579.

Hon-Stan Philip Wong, David J. Frank and Paul M. Solomon, IRM, T. J. Watzot, Resourch Contex, Verbrown Heights, New York 10598, USA, 407-410 pp.

Mohd Vicum, O., A. Zaiki, Y. Syanisuri, Y. Melisukei Razman and A. M. Abiln' Futah. 2008. In Pres-Proceeding of IEEE International Conference on RF and Microways.

M. N. Os man yeled.

The Wolk Kinn, Hunker Kim and Kweyre Lee. 2004. IEEE Journal of Solid State Circuits 33(1):223-229.

- Tarry Dao. 2004. In Proceeding of IBBE International Conference on Integrated Circuit Design and Technology 90 pp.

- Xu, D., T. Broki, T. Sperston, Y. Umoda, Y. Yamane and Y. Ishii. 1998. Distronics Letters 34(16):16-4-1615.