# A SIMULATION STUDY OF SHORT CHANNEL EFFECTS IN CONVENTIONAL AND LIGHTLY-DOPED-DRAIN (LDD) P-MOSFETS

N. SOIN, D. ABD HADI

Department of Electrical Engineering, Faculty of Engineering, University of Malaya, Kuala Lumpur, Malaysia

Abstract This paper presents the comparative study of the short channel effects on both conventional and lightly doped drain (LDD) pMOSFETs. This includes the parametric study of both structures in order to determine the profile of the threshold voltage and leakage current due to the short channel effects. In this study, two critical parameters of the short channel devices were investigated including the channel length (L) and the oxide thickness  $(T_{ox})$ . The significant effects were observed in the device especially on the leakage current mechanism includes substrate and drain currents when these two critical parameters have been scaled down. Apart from that, the influence of device processing parameter namely, source/drain ion implantation dose on the leakage current mechanism had been investigated

KEYWORDS: Short channel effects, leakage current, PMOSFET, Lightly doped drain, channel length, oxide thickness

### Introduction

Reliability of deep submicrometer for n and p channel MOSFET's is a mandatory issue for device scaling and much effort had been made to investigate device degradation (Kaga, 1988). Most of the studies focus on NMOSFETs since the short channel effects are said to be more significant in that particular device compared to PMOSFETs due to larger ionization of electrons in NMOSFET than holes in PMOSFETs (Picher et al., 1999). However, the hot carrier degradation has to be taken into account for PMOSFET with a submicrometer channel length (Picher et al., 1999). The main purpose of this study is to compare the short channel effects on both conventional and LDD PMOSFETs and investigate the capability of the LDD PMOSFET structure in reducing these effects in terms of leakage current and threshold voltage.

Simulation and Device Conditions

Simulation study of short channel effects on the conventional and Lightly Doped Drain (LDD) PMOSFET structures has been conducted using MINIMOS 6.1 (Picher et al., 1999). The 2-D and AVAL models from MINIMOS 6.1 have been used in this simulation. The features of the simulated LDD PMOSFET structure are listed below:

$: 5.5 \times 10^{-7} \text{ cm}$ Gate Oxide

Gate Material : p-doped polysilicon (0.55 V)

Channel Width  $1.0 \times 10^{-4} \text{ cm}$

Channel Implantation : Arsenic,  $1.7 \times 10^{12}$  cm  $^{-2}$ , 10 keV : Arsenic,  $8.0 \times 10^{12}$  cm  $^{-2}$ , 35 keV

Correspondence: Norhayati Soin, Department of Electrical Engineering, Faculty of Engineering, University of Malaya, Kuala Lumpur, Malaysia

UMT, 2007

Source/Drain Doping Profile

```

: p^+ region; Boron, 8.0 \times 10^{15} cm ^{-2}, 95 keV, , XOFF = 50.0 \times 10^{-7} cm : p^- region; Boron, 7.0 \times 10^{14} cm ^{-2}, 20 keV

```

: Bulk Doping;  $1.0\times10^{16}$  cm  $^{-3}$

To simulate the conventional PMOSFET structure, the features are the same except for the non-existing of  $p^{-}$  region in the simulated device. Two biased conditions have been considered in this study as stated below:

```

i. Condition I: V_G = -2.0 \text{ V} and V_D = -0.1 \text{ V}

ii. Condition II: V_G = -2.5 \text{ V} and V_D = -5.0 \text{ V}

```

In both conditions, the source and substrate were connected to the ground.

### Results and Discussion

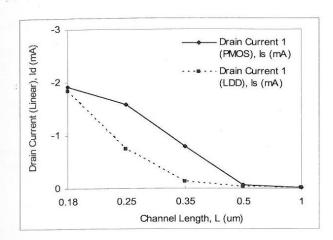

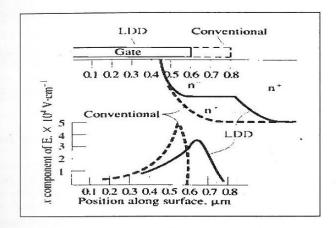

It was found that as the channel length decreased from 1  $\mu$ m to 0.18  $\mu$ m, the drain current increased for both conventional and LDD structures as shown in Figure 1. By comparing the amount of drain current, it was found that the LDD structure managed to reduce the short channel effects compared to the conventional structure since the amount of the drain current for LDD was less than the conventional structure. This is because of the lightly doped regions in the LDD structure in which the magnitude of the electric field at the oxide-semiconductor interface is less than in the conventional structure as shown in Fig. 2. This phenomenon is clearly described in Fig. 2 which shows the physical geometries of a conventional  $n^+$  drain contact and LDD structure superimposed on the same plot.

Besides, the lightly doped regions can contribute to an additional mechanism to the difference between sources and drain resistances ( $R_d$ - $R_s$ ) and also can increase effective channel of the LDD MOSFET device (Md. Rofiqul Hassan *et al.*, 1997). The ( $R_d$ - $R_s$ ) value can be obtained by the given equation [1]:

$$\left(R_d - R_s\right) = \frac{V_{gi} - V_{gn}}{I_D \left(1 + \frac{dV_T}{dV_{SB}}\right)}$$

(1)

where,  $V_{\rm gn}$  and  $V_{\rm gi}$  are the intrinsic gate-source voltages in the normal and inverse mode respectively. The term  $dV_{\rm T}/dV_{\rm SB}$  accounts for the dependence of the threshold voltage with respect to the body voltage,  $V_{\rm SB}$ . From equation (1) it clearly shows that the relationship between  $(R_{\rm d}-R_{\rm s})$  and the drain current,  $I_{\rm D}$  whereas the  $(R_{\rm d}-R_{\rm s})$  is inversely proportional to  $I_{\rm D}$ . As  $(R_{\rm d}-R_{\rm s})$  is increased in the LDD PMOSFET, the drain current will decrease due to the presence of the lightly doped regions that has been introduced to the  $(R_{\rm d}-R_{\rm s})$ . This is one of the reasons that explain the result as shown in Fig. 1. For the LDD PMOSFET, it can be seen that the drain and substrate currents decreased as compared to that of the conventional structure.

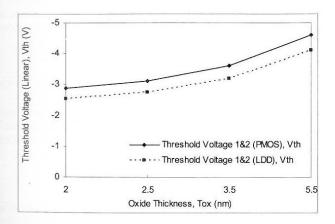

Several studies have found out that by scaling down the channel length, the oxide thickness will simultaneously be scaled (Young Jin Choi, 1998; Richard C. Jaeger, 2002). Another conclusion made from the previous study stated that the oxide thickness is strongly dependent on the threshold voltage for both structures (Conventional PMOSFET and LDD PMOSFET), especially for the LDD PMOSFET structure (Md. Rofiqul Hassan *et al.*, 1997). Figure 3 shows that for both structures, the trend of  $V_{\rm TH}$  versus  $T_{\rm ox}$  is very similar except for their magnitudes. It can be seen from Fig. 3 that the threshold voltage of the LDD PMOSFET is less than the threshold voltage of the conventional structure. This is due to the threshold voltage that is determined from the inversion mechanism in the n-type substrate, but not from the make up of the drain and source region (Young Jin Choi, 1998).

Figure 1. The graph of linear drain current versus channel length when  $T_{ox} = 2$  nm

Figure 2. Magnitude of the electric field at the Si-SiO<sub>2</sub> interface as a function of distance

Figure 3. Graph of threshold voltage versus oxide thickness for both structures

Journal of Sustain. Sci. & Mngt., 2007 Vol. 2(1): 53-56

N. Soin & D. Abd Hadi

### Conclusion

Overall, it was found that the LDD PMOSFET effectively reduced the electric field near the drain region and consequently minimized leakage current such as substrate currents. Besides, the LDD structure also improved the threshold voltage in such device.

## Acknowledgements

The authors would like to thank the Institute for Microelectronics, Vienna, Belgium for sponsoring TCAD simulation tools (MINIMOS 6.1) for the project titled "MOSFETs Reliability".

### References

- Donald. A. Neamen, 1997. Semiconductor Physics and Devices: Basic Principles. 2<sup>nd</sup> edn. McGraw Hill, New York.

- Md. Rofiqul Hassan, J. J. Liou, A. Ortiz-Conde, F. J. G. Sanchez and E. G. Fernandes. 1997. Drain and Source Resistances of Short-Channel LDD MOSFET's. Solid-States Electronics 41(5):778-780

- Md. Rofiqul Hassan, J. J. Liou and A. Ortiz-Conde. 1997. Gate Oxide Thickness Dependence of LDD MOSFET Parameters. Solid-State Electronics 41(8):1199-1201.

- Picher, P., H. Poztl, A. Schutz and S. Selberherr. 1999. MINIMOS 6.1 User Guide. Technical University Vienna.

- Richard C. Jaeger. 2002. Introduction to Microelectronic Fabrication. 2<sup>nd</sup> edn. Prentice Hall, New York.

- Toru Kaga. 1998. Effect of Lightly Doped Drain Structure with Optimum Ion Dose on p-Channel MOSFET's. IEEE Transactions on Electron Devices 35(12):2384-2390.

- Young Jin Choi. 1998. CMOSFET below 0.1 μm: Suppression of Short Channel Effect, Seoul National University.